可分为CCD图像传感器和CMOS图像传感器。 特别是CMOS图像传感器(CIS)不仅被搭载于

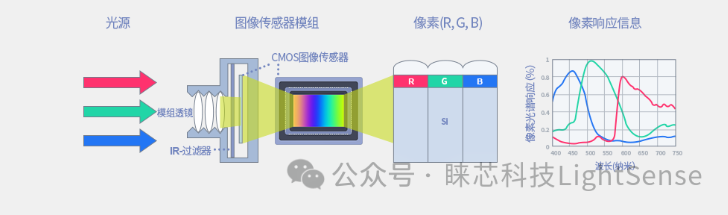

基于CMOS的图像传感器的工作过程如下: 当可见光波长范围(400-700纳米)的光能聚集在硅衬底的(PD)时,硅表面接收光能形成电子-空穴对(electron-hole pair)。 在此过程中产生的电子通过浮动扩散(FD)转换成电压,然后再通过模拟到数字转换器ADC)转换为数字数据。 为了制造出使这一系列流程成为可能的CIS产品,需要采用CIS特有的、有别于半导体存储器的关键制造工艺技术。此类工艺技术可分为以下五大类:

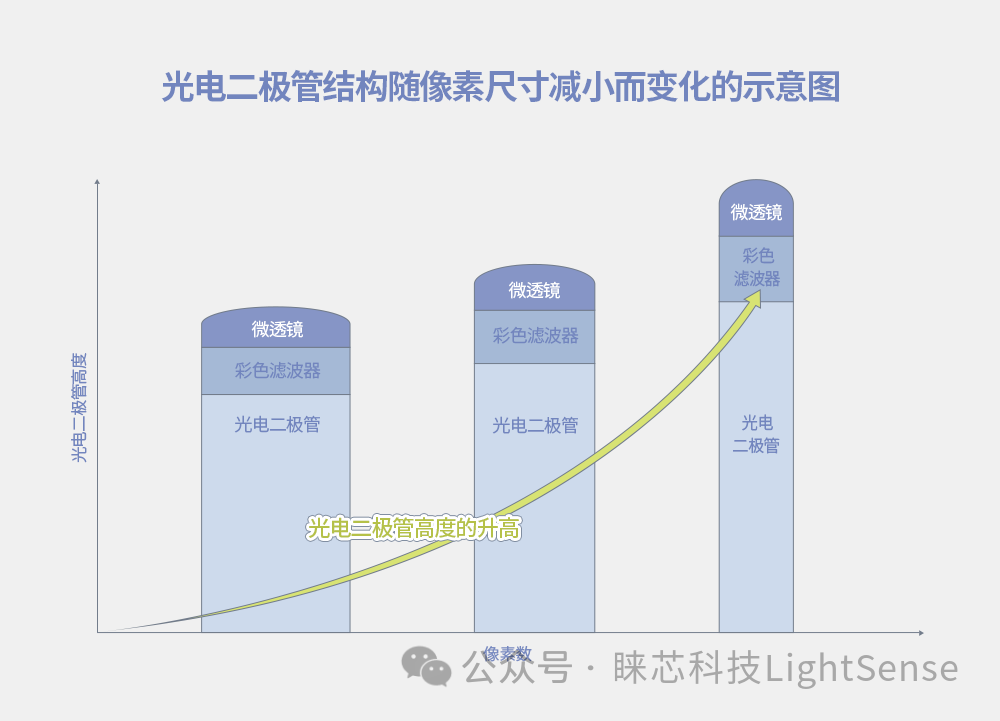

在相同的芯片尺寸上要增加像素数量,就需要不可避免地缩小单一像素的尺寸。深层光电二极管的形成是防止图像质量下降的关键技术。为了在更小的像素中确保足够的满阱容量(full well capacity, FWC),与半导体存储器相比,CIS需要采用难度更高的图像形成技术。尤其需要确保高纵横比(>

15:1)植入掩码(implant MASK)工艺技术,以阻止高能量离子的植入;事实上,目前纵横比在业内有逐步提高的趋势。

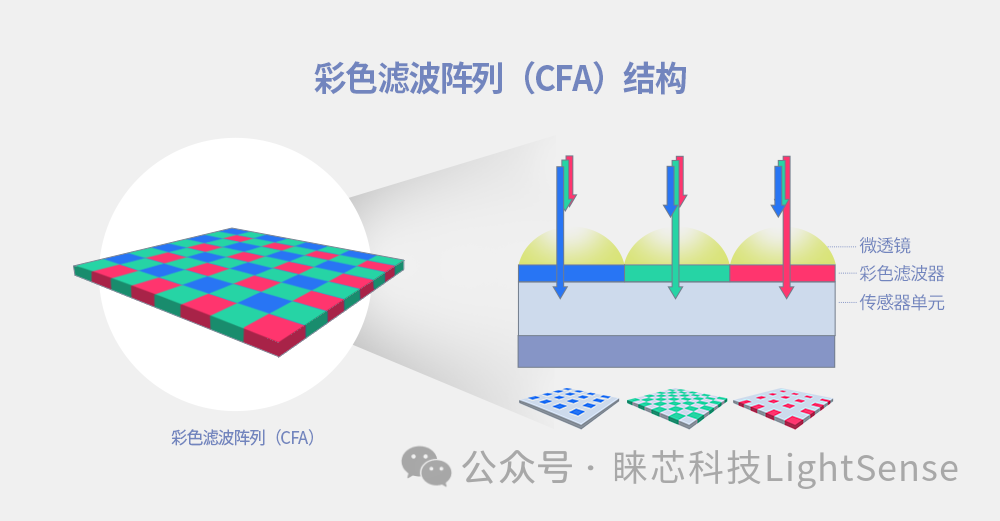

彩色滤波阵列是有别于半导体存储器制造工艺的CIS独有的工艺 。CFA工艺一般由彩色滤波器(CF)和微透镜(ML)组成,前者可将入射光过滤成红、绿、蓝各波长范围,后者可提高光凝聚效率。为了获得优良的图像品质,开发和评估R/G/B彩色素材并开发相关技术以优化形状、厚度等工艺条件非常重要。

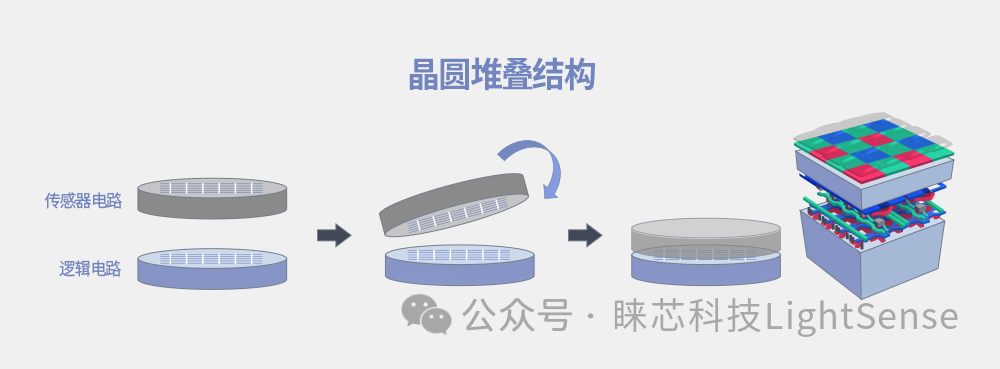

晶圆堆叠是指将两个晶圆连接在一起。这是制作高像素、高清晰度的CIS产品的必备技术。对于高像素CIS产品,像素阵列和逻辑电路分别在个别晶圆上形成。这些晶圆在工艺期间被连接在一起,而这一过程被称为“晶圆粘结(wafer bonding)”。像素阵列和逻辑电路的分离意味着制造成本的增加,但同时也意味着可以在同等晶圆面积上生产更多芯片;不仅如此,这还有助于提高产品的性能。因此,这是目前大多数CIS芯片厂商所采用的技术。晶圆堆叠技术正以各种形式不断发展。近年来,晶圆堆叠技术也被应用于半导体存储器领域,促进了产品性能的提升。

控制金属污染是CIS产品开发和量产过程中最基本的前提条件之一。由于CIS产品对污染的敏感度是存储器产品的数倍,且污染会直接影响CIS产品的良品率和质量,因此CIS的生产必须采用各种污染控制技术。另一个重要因素是等离子体损伤控制。由于图像属性的损坏(如热像素)是在工艺过程中造成的损伤而发生的,因此有必要对关键工艺进行精确管理。

缺陷解析 /

过去存在着像素大,信噪比小,分辨率低这些缺点,一直无法和CCD技术抗衡。但是随着大规模集成电路技

过去存在着像素大,信噪比小,分辨率低这些缺点,一直无法和CCD技术抗衡。但是随着大规模集成电路技术的不断发展,过去

)。MC502ER支持 VGA (640Hx480V) 分辨率,并采用MagnaChip 的0.13微米

过去存在着像素大,信噪比小,分辨率低这些缺点,一直无法和CCD技术抗衡。但是随着大规模集成电路技术的不断发展,过去

【米尔-全志T113-i开发板试用】JPG硬件编码的实现、YUV转换neon加速和对比测试

Copyright © 2019 ayx游戏官网(china)AYX在线最新官网下载 地址:江苏省昆山市周庄镇高科技产业园秀园路